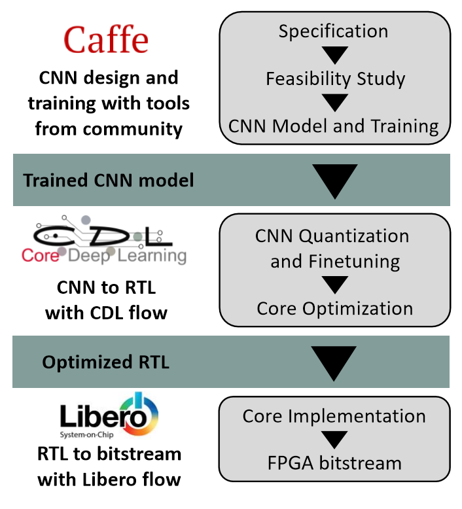

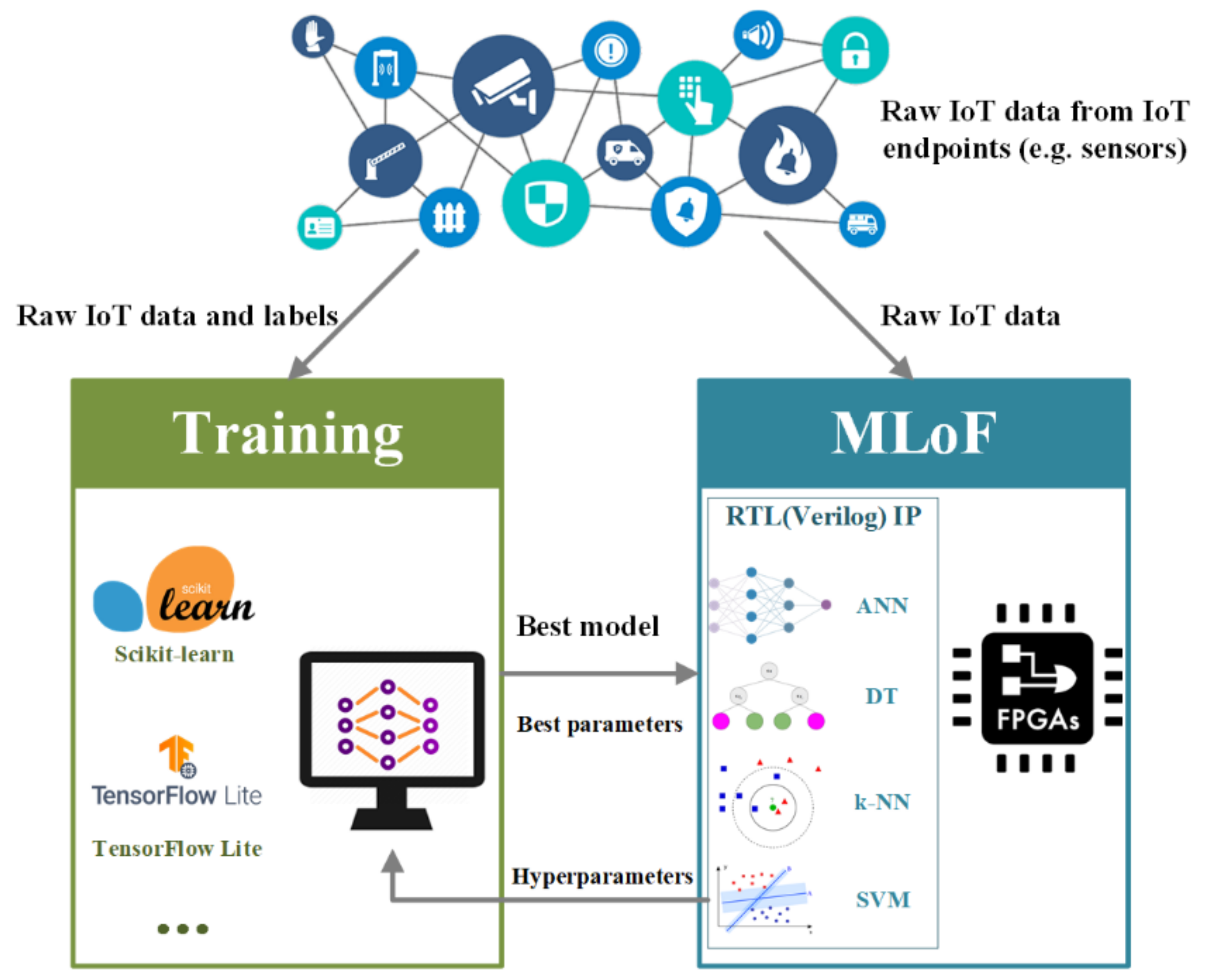

Applied Sciences | Free Full-Text | MLoF: Machine Learning Accelerators for the Low-Cost FPGA Platforms

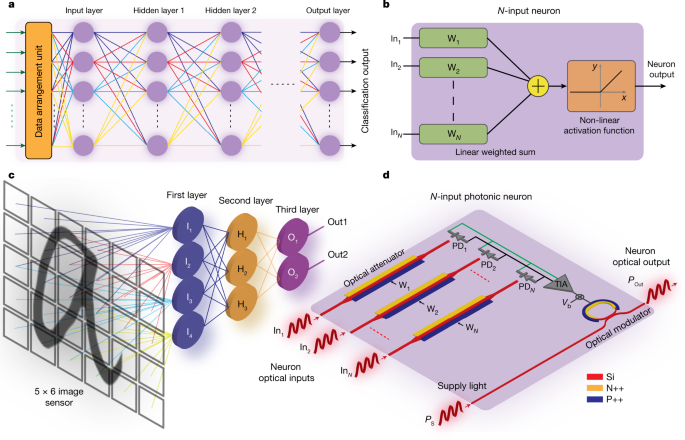

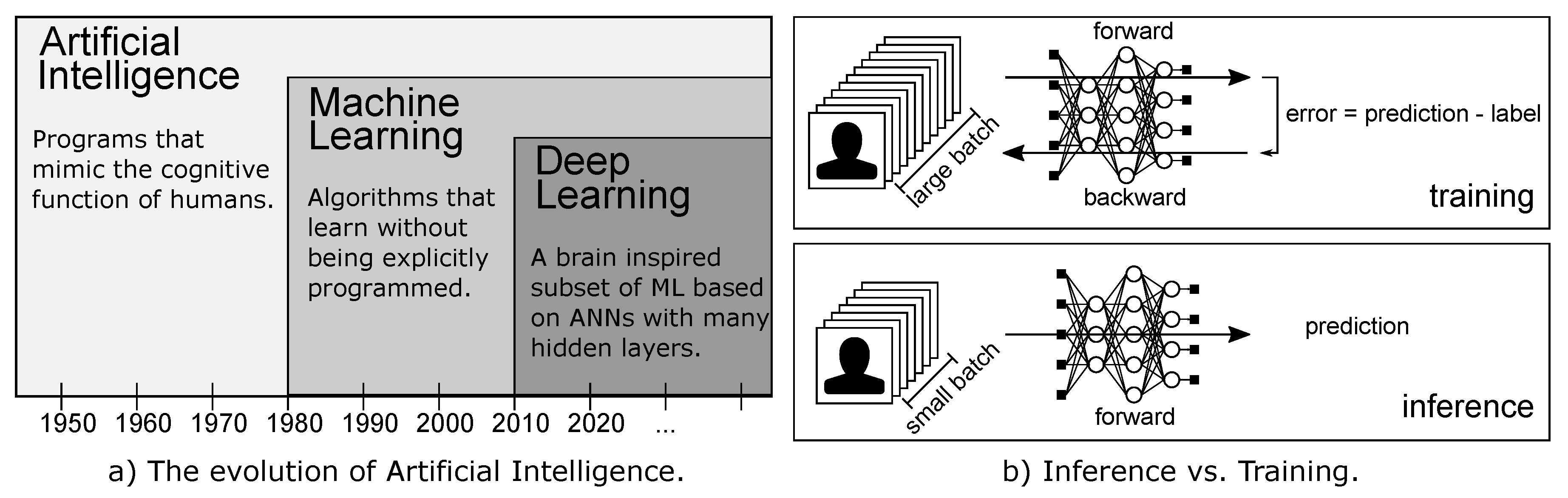

Future Internet | Free Full-Text | An Updated Survey of Efficient Hardware Architectures for Accelerating Deep Convolutional Neural Networks